RISC (Multistate and Pipeline) Microprocessor Design

Reduced Instruction Set Architecture

This is the IITB RISC microprocessor design that we did as a course project for EE309, Microprocessors.

The project repository can be found here.

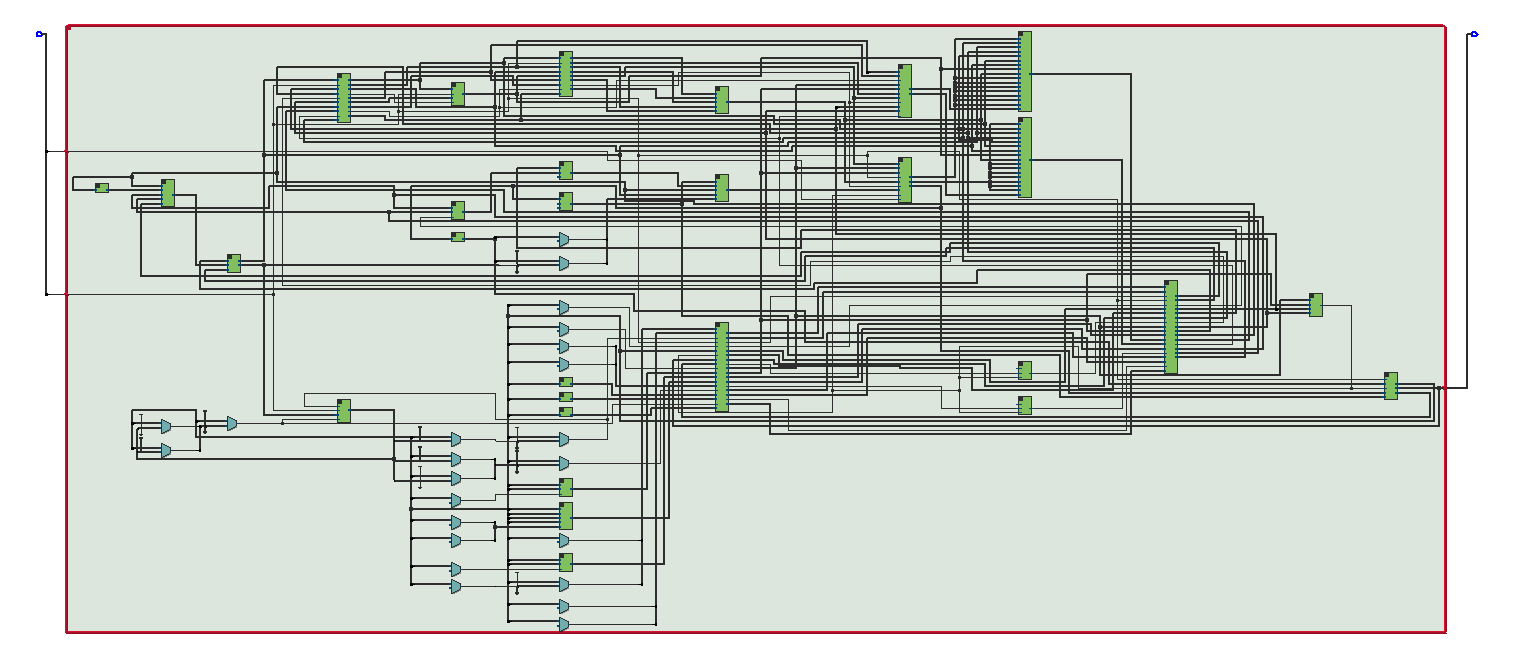

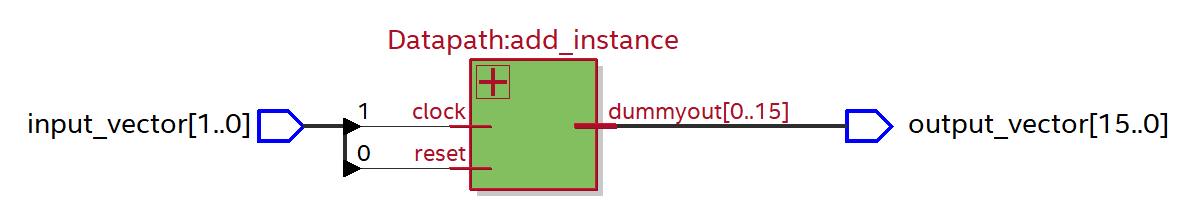

MultiState Design

Designed a multistate implementation of IITB-RISC, a 16-bit computer based on the Little Computer Architecture. The IITB-RISC is an 8-register, 16-bit computer system. It has 8 general-purpose registers (R0 to R7). Register R7 always stores the Program Counter. This architecture uses a condition code register with two flags: Carry flag (C) and Zero flag (Z). The IITB-RISC is simple but general enough to solve complex problems. The architecture allows predicated instruction execution and multiple load and store execution. There are three machine-code instruction formats (R, I, and J type) and a total of 17 instructions.

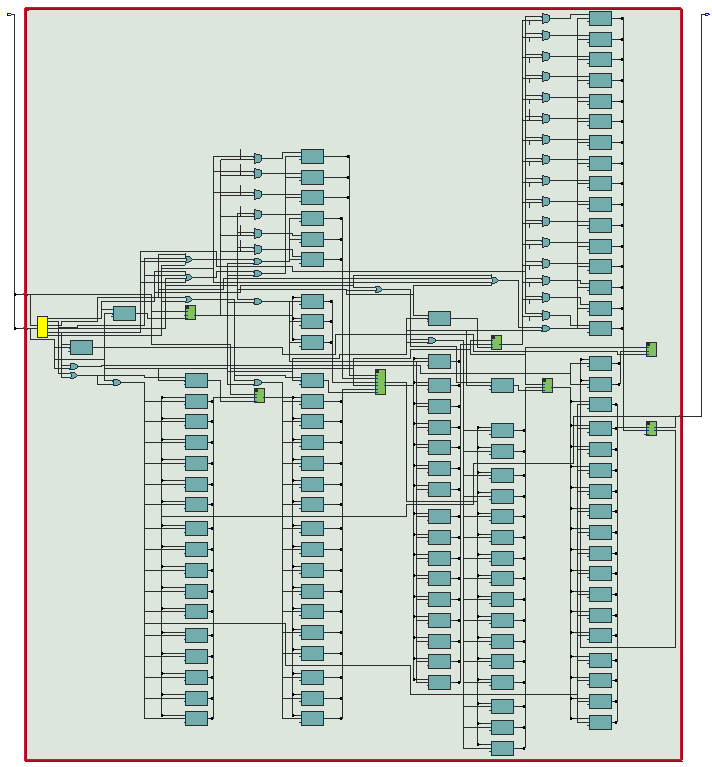

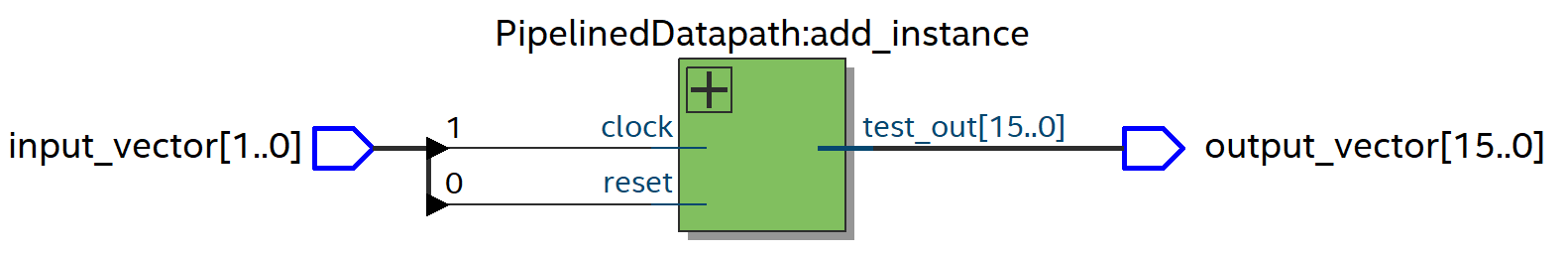

Pipelined Design

Implemented a 6 stage pipelined processor, IITB-RISC-22, whose instruction set architecture was provided. IITB-RISC is a 16-bit very simple computer developed for teaching that is based on the Little Computer Architecture. The IITB-RISC-22 is a 16-bit computer system with 8 registers. It follows the standard 6 stage pipelines (Instruction fetch, instruction decode, register read, execute, memory access, and write back). The architecture is optimized for performance, i.e., includes hazard mitigation techniques. Hence, it has a forwarding and branch prediction technique